Penapis anti-aliasing dan penstabil voltan

Penapis pelicin direka untuk mengurangkan riak voltan diperbetulkan. Pelicinan riak dinilai oleh faktor pelicinan q.

Penapis pelicin direka untuk mengurangkan riak voltan diperbetulkan. Pelicinan riak dinilai oleh faktor pelicinan q.

Elemen utama penapis melicinkan ialah kapasitor, induktor dan transistor yang rintangannya berbeza untuk arus terus dan arus ulang alik.

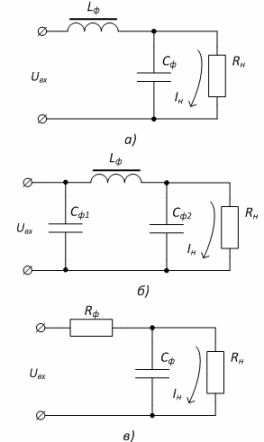

Bergantung pada jenis elemen penapis, perbezaan dibuat antara penapis kapasitif, induktif dan elektronik. Mengikut bilangan pautan penapisan, penapis dibahagikan kepada pautan tunggal dan berbilang pautan.

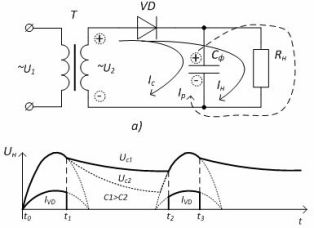

Penapis kapasitif ialah kapasitor dengan kapasiti besar yang disambungkan selari dengan perintang beban Rn. Kapasitor mempunyai rintangan DC yang tinggi dan rintangan AC yang rendah. Mari kita pertimbangkan operasi penapis pada contoh litar penerus separuh gelombang (Rajah 1, a).

Rajah 1-Penerus separuh gelombang fasa tunggal dengan penapis kapasitif: a) litar b) gambar rajah pemasaan operasi

Apabila gelombang separuh positif mengalir dalam selang masa t0 — t1 (Rajah 2.63, b), arus beban (arus diod) dan aliran arus cas kapasitor.Kapasitor dicas dan pada masa t1 voltan dalam kapasitor melebihi penurunan voltan penggulungan sekunder - diod ditutup dan dalam selang masa t1 - t2 arus dalam beban disediakan oleh nyahcas kapasitor. Che. arus dalam beban mengalir secara berterusan, yang dengan ketara mengurangkan riak voltan diperbetulkan.

Lebih besar kapasitansi kapasitor Cf, lebih kecil pengujaan. Ini ditentukan oleh masa nyahcas kapasitor — pemalar masa nyahcas τ = СfRн. Pada τ> 10, pekali pelicinan ditentukan oleh formula q = 2π fc m Cf Rn, di mana fc ialah kekerapan rangkaian, m ialah bilangan separuh tempoh voltan diperbetulkan.

Adalah disyorkan untuk menggunakan penapis kapasitif dengan perintang beban RH rintangan tinggi pada kuasa beban rendah.

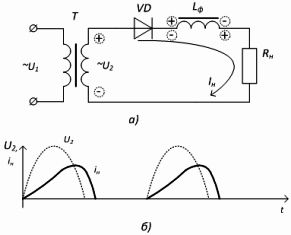

Penapis induktif (tercekik) disambung secara bersiri dengan Rn (Rajah 3, a). Kearuhan mempunyai rintangan DC yang rendah dan rintangan AC yang tinggi. Pelicinan riak adalah berdasarkan fenomena induksi diri, yang pada mulanya menghalang arus daripada meningkat, dan kemudian menyokongnya dengan penurunannya (Rajah 2, b).

Rajah 2-Penurus separuh gelombang fasa tunggal dengan penapis induktif: a) litar, b) gambar rajah pemasaan operasi

Penapis induktif digunakan dalam penerus kuasa sederhana dan tinggi, iaitu, dalam penerus yang beroperasi dengan arus beban yang besar.

Pekali pelicinan ditentukan oleh formula: q = 2π fs m Lf / Rn

Operasi penapis kapasitif dan induktif adalah berdasarkan fakta bahawa semasa aliran arus yang digunakan oleh rangkaian, kapasitor dan induktor menyimpan tenaga, dan apabila tiada arus dari rangkaian, atau ia berkurangan, unsur-unsur memberi penutupan tenaga yang disimpan, mengekalkan arus (voltan ) dalam beban.

Penapis berbilang simpang menggunakan sifat pelicinan kedua-dua kapasitor dan induktor. Dalam penerus kuasa rendah, di mana rintangan perintang beban adalah beberapa kOhm, bukannya pencekik Lf, perintang Rf dimasukkan, yang mengurangkan jisim dan dimensi penapis dengan ketara.

Rajah 3 menunjukkan jenis penapis tangga LC dan RC.

Rajah 3-Penapis berbilang simpang: a) LC berbentuk L, b) LC berbentuk U, c) Penapis RC

Penstabil direka untuk menstabilkan voltan malar (arus) beban semasa turun naik voltan sesalur dan perubahan arus yang digunakan oleh beban.

Penstabil dibahagikan kepada penstabil voltan dan arus, serta parametrik dan pampasan. Kestabilan voltan keluaran dinilai oleh faktor penstabilan Kst.

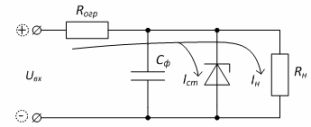

Penstabil parametrik berdasarkan penggunaan elemen dengan ciri bukan linear - diod zener semikonduktor Voltan diod zener hampir malar dengan perubahan ketara dalam arus terbalik melalui peranti.

Litar penstabil parametrik ditunjukkan dalam Rajah 4. Voltan input UBX diagihkan antara perintang had Rlim dan VD diod zener yang disambung selari dan perintang beban Rn.

Rajah 4 — Penstabil parametrik

Apabila voltan masukan meningkat, arus melalui diod zener akan meningkat, yang bermaksud bahawa arus melalui perintang pengehad akan meningkat dan penurunan voltan yang lebih besar akan berlaku di atasnya, dan voltan beban akan kekal tidak berubah.

Penstabil parametrik mempunyai Kst tertib 20-50. Kelemahan penstabil jenis ini ialah arus penstabilan rendah dan kecekapan rendah.

Penstabil parametrik digunakan sebagai sumber voltan tambahan, dan juga apabila arus beban kecil — tidak lebih daripada ratusan miliamp.

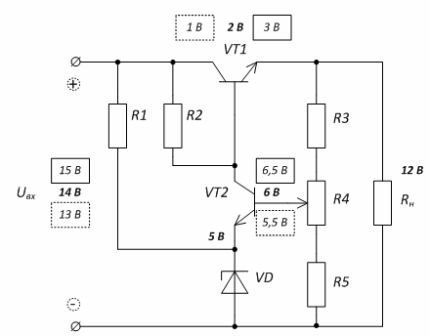

Penstabil pampasan menggunakan rintangan pembolehubah transistor sebagai perintang pengehad. Apabila voltan masukan meningkat, rintangan transistor juga meningkat, pada masa yang sama, apabila voltan berkurangan, rintangan berkurangan. Dalam kes ini, voltan dalam beban kekal tidak berubah.

Litar penstabil transistor ditunjukkan dalam Rajah 5. Prinsip pengawalan voltan keluaran URn adalah berdasarkan perubahan dalam kekonduksian transistor pengawalseliaan VT1.

Rajah 5 — Skema pengatur voltan pampasan

Litar perbandingan voltan dan penguat DC dipasang pada transistor VT2. Litar pengukur R3, R4, R5 disertakan dalam litar asasnya, dan sumber voltan rujukan R1VD disertakan dalam litar pemancar.

Sebagai contoh, apabila voltan masukan meningkat, keluaran juga akan meningkat, yang akan membawa kepada peningkatan voltan pada asas transistor VT2, manakala pada masa yang sama potensi pemancar VT2 akan kekal sama.Ini akan membawa kepada peningkatan dalam arus asas, dan oleh itu arus pengumpul transistor VT2 — potensi asas transistor VT1 akan berkurangan, transistor akan ditutup dan penurunan voltan yang lebih besar akan berlaku padanya, dan voltan keluaran akan kekal tidak berubah.

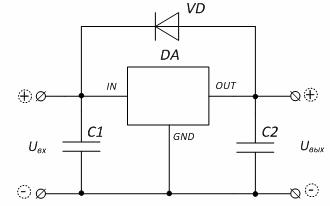

Hari ini, penstabil dihasilkan dalam bentuk litar bersepadu. Skim tipikal untuk menghidupkan penstabil bersepadu ditunjukkan dalam Rajah 6.

Rajah 6 — Skema tipikal untuk menghidupkan penstabil voltan terbina dalam

Penetapan output litar mikro penstabil: «IN» — input, «OUT» — output, «GND» — biasa (kes). Jika penstabil boleh laras, maka terdapat output «ADJ» — pelarasan.

Pemilihan penstabil adalah berdasarkan nilai voltan keluaran, arus beban maksimum dan julat variasi voltan masukan.