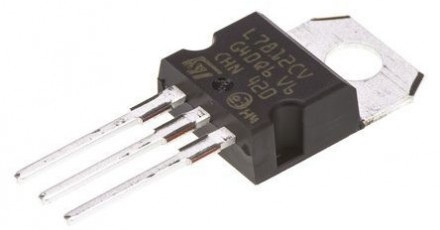

Penstabil voltan linear — tujuan, parameter asas dan litar pensuisan

Mungkin hari ini, tiada papan elektronik boleh melakukannya tanpa sekurang-kurangnya satu sumber voltan malar malar. Dan selalunya pengawal selia voltan linear dalam bentuk litar mikro berfungsi sebagai sumber sedemikian. Tidak seperti penerus dengan pengubah, di mana voltan dalam satu cara atau yang lain bergantung pada arus beban dan boleh berbeza sedikit untuk pelbagai sebab, litar mikro bersepadu - penstabil (pengawal selia) mampu memberikan voltan malar dalam julat yang ditakrifkan dengan tepat. arus beban.

Litar mikro ini dibina berdasarkan kesan medan atau transistor bipolar, beroperasi secara berterusan dalam mod aktif. Sebagai tambahan kepada transistor pengawal selia, litar kawalan juga dipasang pada kristal litar mikro penstabil linear.

Dari segi sejarah, sebelum menjadi mungkin untuk mengeluarkan penstabil sedemikian dalam bentuk litar mikro, terdapat persoalan untuk menyelesaikan masalah kestabilan suhu parameter, kerana dengan pemanasan semasa operasi, parameter nod litar mikro akan berubah.

Penyelesaiannya datang pada tahun 1967, apabila jurutera elektronik Amerika Robert Widlar mencadangkan litar penstabil di mana transistor pengawal selia akan disambungkan antara sumber voltan masukan yang tidak terkawal dan beban, dan penguat ralat dengan voltan rujukan pampasan suhu akan hadir dalam litar kawalan. Akibatnya, populariti penstabil bersepadu linear dalam pasaran melonjak dengan pantas.

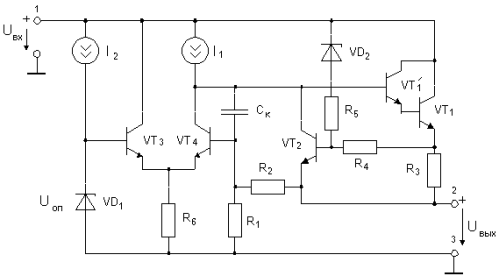

Lihat foto di bawah. Ditunjukkan di sini ialah rajah dipermudah bagi pengatur voltan linear (seperti LM310 atau 142ENxx). Dalam skema ini, penguat operasi maklum balas voltan negatif bukan penyongsangan, menggunakan arus keluarannya, mengawal tahap membuka kunci transistor pengawal selia VT1, disambungkan dalam litar dengan pengumpul biasa - pengikut pemancar.

Op-amp itu sendiri dikuasakan oleh sumber input dalam bentuk voltan positif unipolar. Dan walaupun voltan negatif tidak sesuai untuk bekalan di sini, voltan bekalan op-amp boleh digandakan tanpa masalah, tanpa rasa takut beban berlebihan atau kerosakan.

Kesimpulannya ialah maklum balas negatif yang mendalam meneutralkan ketidakstabilan voltan input, nilai yang dalam litar ini boleh mencapai 30 volt. Jadi, voltan keluaran tetap berkisar antara 1.2 hingga 27 volt, bergantung pada model cip.

Litar mikro penstabil secara tradisinya mempunyai tiga pin: input, biasa dan output.Rajah menunjukkan litar tipikal penguat pembezaan sebagai sebahagian daripada litar mikro untuk mendapatkan voltan rujukan Diod Zener digunakan.

Dalam pengawal selia voltan rendah, rujukan voltan diperoleh pada jurang, seperti yang pertama kali dicadangkan oleh Widlar dalam pengawal selia bersepadu linear pertamanya, LM109. Pembahagi dipasang dalam litar maklum balas negatif perintang R1 dan R2, dengan tindakan yang mana voltan keluaran ternyata hanya berkadar dengan voltan rujukan mengikut formula Uout = Uvd (1 + R2 / R1).

Perintang R3 dan transistor VT2 yang dibina ke dalam penstabil berfungsi untuk mengehadkan arus keluaran, jadi jika voltan pada perintang pengehad arus melebihi 0.6 volt, maka transistor VT2 akan terbuka serta-merta, yang akan menyebabkan arus asas transistor kawalan utama VT1 menjadi. terhad. Ternyata arus keluaran dalam mod operasi biasa penstabil adalah terhad kepada 0.6 / R3. Kuasa yang hilang oleh transistor pengawal selia akan bergantung pada voltan masukan dan akan bersamaan dengan 0.6 (Uin — Uout) / R3.

Jika atas sebab tertentu litar pintas berlaku pada output penstabil bersepadu, maka kuasa yang hilang pada kristal tidak boleh dibiarkan seperti sebelumnya, berkadar dengan perbezaan voltan dan berkadar songsang dengan rintangan perintang R3. Oleh itu, litar mengandungi elemen pelindung - diod zener VD2 dan perintang R5, operasi yang menetapkan tahap perlindungan semasa bergantung pada perbezaan voltan Uin -Uout.

Dalam graf di atas, anda dapat melihat bahawa arus keluaran maksimum bergantung pada voltan keluaran, oleh itu litar mikro penstabil linear dilindungi dengan pasti daripada beban lampau.Apabila perbezaan voltan Uin-Uout melebihi voltan penstabilan diod zener VD2, pembahagi perintang R4 dan R5 akan mencipta arus yang mencukupi di pangkalan transistor VT2 untuk mematikannya, yang seterusnya akan menyebabkan had arus asas untuk meningkatkan transistor pengawal selia VT1.

Model terkini pengawal selia linear, seperti ADP3303, dilengkapi dengan perlindungan beban lampau haba apabila arus keluaran turun dengan mendadak apabila kristal dipanaskan hingga 165 ° C. Kapasitor dalam rajah di atas diperlukan untuk menyamakan frekuensi.

Dengan cara ini, mengenai kapasitor. Adalah menjadi kebiasaan untuk menyambungkan kapasitor dengan kapasiti minimum 100 nf ke input dan output penstabil bersepadu untuk mengelakkan pengaktifan palsu litar dalaman litar mikro. Sementara itu, terdapat apa yang dipanggil penstabil capless, seperti REG103, yang mana tidak perlu memasang kapasitor penstabil pada input dan output.

Sebagai tambahan kepada penstabil linear dengan voltan keluaran tetap, terdapat juga penstabil dengan voltan keluaran boleh laras untuk penstabilan. Di dalamnya, pembahagi perintang R1 dan R2 hilang, dan pangkalan transistor VT4 dibawa keluar ke kaki berasingan cip untuk menyambungkan pembahagi luaran, seperti dalam cip 142EN4.

Penstabil yang lebih moden, di mana penggunaan semasa litar kawalan dikurangkan kepada beberapa puluh mikroamp, seperti LM317, hanya mempunyai tiga pin.Untuk bersikap adil, kami perhatikan bahawa hari ini terdapat juga pengawal selia voltan berketepatan tinggi seperti TPS70151, yang, disebabkan kehadiran beberapa pin tambahan, memungkinkan untuk menggunakan perlindungan penurunan voltan pada wayar penyambung, kawalan pelepasan beban, dsb. .

Di atas kita bercakap tentang penstabil voltan positif, berbanding wayar biasa. Skim serupa juga digunakan untuk menstabilkan voltan negatif, cukup hanya untuk mengasingkan voltan keluaran input secara galvani dari titik biasa. Pin keluaran kemudiannya disambungkan ke titik keluaran biasa, dan titik keluaran negatif akan menjadi titik tolak input yang disambungkan ke titik sepunya cip penstabil. Pengatur voltan kekutuban negatif seperti 1168ENxx sangat mudah.

Sekiranya perlu untuk mendapatkan dua voltan sekaligus (kekutuban positif dan negatif), maka untuk tujuan ini terdapat penstabil khas yang memberikan voltan positif dan negatif yang stabil secara simetri pada masa yang sama, cukup hanya untuk menggunakan voltan input positif dan negatif kepada input. Contoh penstabil bipolar tersebut ialah KR142EN6.

Rajah di atas ialah gambar rajah yang dipermudahkan. Di sini, penguat pembezaan # 2 memacu transistor VT2, jadi kesamaan -UoutR1 / (R1 + R3) = -Uop diperhatikan. Dan penguat #1 mengawal transistor VT1 supaya potensi pada persimpangan perintang R2 dan R4 kekal sifar. Jika pada masa yang sama perintang R2 dan R4 adalah sama, maka voltan keluaran (positif dan negatif) akan kekal simetri.

Untuk pelarasan bebas baki antara dua voltan keluaran (positif dan negatif), anda boleh menyambungkan perintang pemangkasan tambahan ke pin khas litar mikro.

Ciri penurunan voltan terkecil bagi litar kawal selia linear di atas ialah 3 volt. Ini agak banyak untuk peranti berkuasa bateri atau bateri dan secara amnya wajar untuk meminimumkan penurunan voltan. Untuk tujuan ini, transistor keluaran dibuat jenis pnp supaya arus pengumpul peringkat pembezaan adalah serentak dengan arus asas transistor pengawal selia VT1. Penurunan voltan minimum kini akan berada pada urutan 1 volt.

Pengawal selia voltan negatif beroperasi dengan cara yang sama dengan penurunan yang minimum. Sebagai contoh, pengawal selia siri 1170ENxx mempunyai penurunan voltan kira-kira 0.6 volt dan tidak terlalu panas apabila dibuat dalam kes TO-92 pada arus beban sehingga 100 mA. Penstabil itu sendiri menggunakan tidak lebih daripada 1.2 mA.

Penstabil sedemikian dikelaskan sebagai rendah droop. Malah penurunan voltan yang lebih rendah dicapai pada pengawal selia berasaskan MOSFET (kira-kira 55 mV pada penggunaan arus cip 1 mA) seperti cip MAX8865.

Sesetengah model penstabil dilengkapi dengan pin tutup untuk mengurangkan penggunaan kuasa peranti dalam mod siap sedia — apabila tahap logik digunakan pada pin ini, penggunaan penstabil dikurangkan kepada hampir sifar (garisan LT176x).

Bercakap tentang penstabil linear integral, mereka perhatikan ciri-ciri mereka, serta parameter dinamik dan tepat.

Parameter ketepatan ialah faktor penstabilan, ketepatan tetapan voltan keluaran, galangan keluaran dan pekali suhu voltan. Setiap parameter ini disenaraikan dalam dokumentasi; ia berkaitan dengan ketepatan voltan keluaran bergantung kepada voltan masukan dan suhu semasa kristal.

Parameter dinamik seperti nisbah penindasan riak dan impedans keluaran ditetapkan untuk frekuensi arus beban dan voltan input yang berbeza.

Ciri-ciri prestasi seperti julat voltan input, voltan keluaran terkadar, arus beban maksimum, pelesapan kuasa maksimum, perbezaan voltan input dan output maksimum pada arus beban maksimum, arus tanpa beban, julat suhu operasi, semua parameter ini mempengaruhi pilihan satu atau yang lain.penstabil untuk litar tertentu.

Ciri-ciri pengawal selia voltan linear

Berikut ialah litar biasa dan paling popular untuk memasukkan penstabil linear:

Jika perlu untuk meningkatkan voltan keluaran penstabil linear dengan voltan keluaran tetap, diod zener ditambah secara bersiri ke terminal biasa:

Untuk memaksimumkan arus keluaran yang dibenarkan, transistor yang lebih berkuasa disambungkan selari dengan penstabil, menjadikan transistor pengawal selia di dalam litar mikro menjadi sebahagian daripada transistor komposit:

Sekiranya perlu untuk menstabilkan arus, penstabil voltan dihidupkan mengikut skema berikut.

Dalam kes ini, penurunan voltan merentasi perintang akan sama dengan voltan penstabilan, yang akan membawa kepada kerugian yang ketara jika voltan penstabilan tinggi.Dalam hal ini, adalah lebih sesuai untuk memilih penstabil untuk voltan keluaran yang paling rendah, seperti KR142EN12 untuk 1.2 volt.