Transistor kesan medan

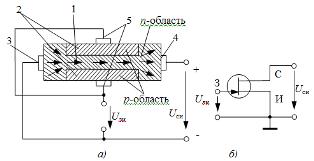

Transistor kesan medan (unipolar) dibahagikan kepada transistor dengan persimpangan p-n kawalan (Rajah 1) dan dengan get terpencil. Peranti transistor kesan medan dengan persimpangan p-n kawalan adalah lebih mudah daripada yang bipolar.

Transistor kesan medan (unipolar) dibahagikan kepada transistor dengan persimpangan p-n kawalan (Rajah 1) dan dengan get terpencil. Peranti transistor kesan medan dengan persimpangan p-n kawalan adalah lebih mudah daripada yang bipolar.

Dalam transistor saluran-n, pembawa cas utama dalam saluran adalah elektron yang bergerak sepanjang saluran dari sumber berpotensi rendah ke longkang berpotensi lebih tinggi, membentuk arus longkang Ic. Voltan terbalik digunakan di antara pintu dan punca FET, yang menyekat persimpangan p-n yang dibentuk oleh kawasan-n saluran dan kawasan-p pintu.

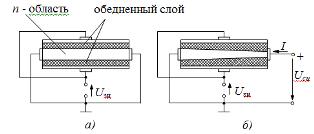

Oleh itu, dalam FET saluran-n, kekutuban voltan yang digunakan adalah seperti berikut: Usi> 0, Usi≤0. Apabila voltan penyekat dikenakan pada simpang pn antara pintu dan saluran (lihat Rajah 2, a), lapisan seragam, habis dalam pembawa cas dan dengan rintangan yang tinggi, muncul di sempadan saluran.

nasi. 1. Struktur (a) dan litar (b) transistor kesan medan dengan get dalam bentuk simpang p-n dan saluran jenis-n; 1,2 - zon saluran dan portal; 3,4,5 - kesimpulan sumber, longkang, penjara

nasi. 2. Lebar saluran dalam transistor kesan medan pada Usi = 0 (a) dan pada Usi> 0 (b)

Ini membawa kepada pengurangan lebar saluran pengalir. Apabila voltan dikenakan di antara punca dan longkang, lapisan penyusutan menjadi tidak sekata (Rajah 2, b), keratan rentas saluran berhampiran longkang berkurangan, dan kekonduksian saluran juga berkurangan.

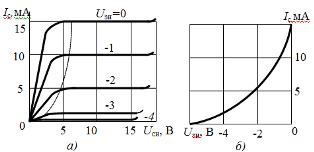

Ciri-ciri VAH bagi FET ditunjukkan dalam Rajah. 3. Di sini, kebergantungan Ic arus longkang pada voltan Usi pada voltan get malar Uzi menentukan ciri keluaran atau longkang transistor kesan medan (Rajah 3, a).

nasi. 3. Output (a) dan pemindahan (b) ciri-ciri volt-ampere transistor kesan medan.

Dalam bahagian awal ciri, arus longkang meningkat dengan peningkatan Umi. Apabila voltan saliran sumber meningkat kepada Usi = Uzap– [Uzi], saluran bertindih dan peningkatan seterusnya dalam hentian Ic semasa (rantau tepu).

Voltan get-ke-sumber Uzi negatif menghasilkan nilai voltan Uc dan Ic arus yang lebih rendah di mana saluran bertindih.

Peningkatan selanjutnya dalam voltan Usi membawa kepada pecahan persimpangan p — n antara pintu gerbang dan saluran dan melumpuhkan transistor. Ciri keluaran boleh digunakan untuk membina ciri pemindahan Ic = f (Uz) (Rajah 3, b).

Dalam bahagian tepu, ia boleh dikatakan bebas daripada voltan Usi. Ia menunjukkan bahawa jika tiada voltan masukan (pintu - longkang), saluran itu mempunyai kekonduksian tertentu dan mengalirkan arus yang dipanggil arus longkang awal Ic0.

Untuk "mengunci" saluran dengan berkesan, adalah perlu untuk menggunakan Uotc voltan mengganggu pada input.Ciri input FET — kebergantungan arus longkang get I3 pada gate — voltan sumber — biasanya tidak digunakan, kerana pada Uzi < 0 persimpangan p-n antara get dan saluran ditutup dan arus get adalah sangat kecil (I3 = 10-8 … 10-9 A), jadi dalam banyak kes ia boleh diabaikan.

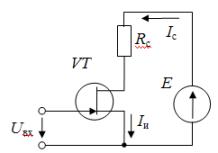

Seperti dalam kes ini transistor bipolar, medan mempunyai tiga litar pensuisan: dengan pintu pagar biasa, longkang dan punca (Rajah 4). Ciri pemindahan IV transistor kesan medan dengan persimpangan p-n kawalan ditunjukkan dalam Rajah. 3, b.

nasi. 4. Skim pensuisan transistor kesan medan sumber biasa dengan persimpangan p-n kawalan

Kelebihan utama transistor kesan medan dengan persimpangan p-n kawalan ke atas yang dwikutub ialah galangan masukan yang tinggi, hingar rendah, kemudahan pengeluaran, penurunan voltan rendah dalam saluran terbuka sepenuhnya. Walau bagaimanapun, transistor kesan medan mempunyai kelemahan seperti perlu bekerja di kawasan negatif I — ciri V, yang merumitkan skema.

Doktor sains teknikal, profesor L.A. Potapov