Pemalar masa litar elektrik — apakah ia dan di mana ia digunakan

Proses berkala adalah sifat semula jadi: siang diikuti oleh malam, musim panas digantikan dengan sejuk, dsb. Tempoh peristiwa ini hampir tetap dan oleh itu boleh ditentukan dengan ketat. Selain itu, kami berhak untuk mendakwa bahawa proses semula jadi berkala yang disebut sebagai contoh tidak menyusut nilai, sekurang-kurangnya dari segi jangka hayat seseorang.

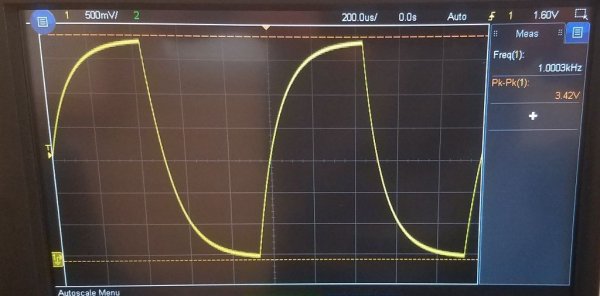

Walau bagaimanapun, dalam teknologi, dalam kejuruteraan elektrik dan elektronik, terutamanya, tidak semua proses adalah berkala dan berterusan. Biasanya, beberapa proses elektromagnet mula-mula meningkat dan kemudian menurun. Selalunya jirim hanya terhad kepada fasa permulaan ayunan, yang tidak mempunyai masa untuk benar-benar meningkatkan kelajuan.

Selalunya dalam kejuruteraan elektrik anda boleh menemui apa yang dipanggil transien eksponen, intipatinya ialah sistem itu hanya berusaha untuk mencapai keadaan keseimbangan, yang akhirnya kelihatan seperti keadaan rehat. Peralihan sedemikian boleh sama ada meningkat atau menurun.

Daya luaran mula-mula membawa sistem dinamik keluar daripada keseimbangan, dan kemudian tidak menghalang pengembalian semula jadi sistem ini kepada keadaan asalnya. Fasa terakhir ini adalah apa yang dipanggil proses peralihan, yang dicirikan oleh tempoh tertentu. Selain itu, proses ketidakseimbangan sistem juga merupakan proses sementara dengan tempoh ciri.

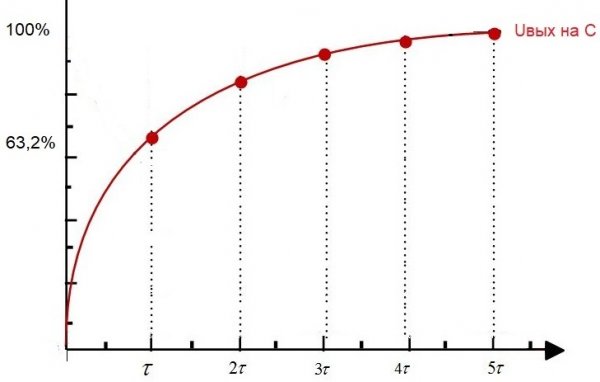

Satu cara atau yang lain, pemalar masa proses sementara, kita panggil ciri masanya, yang menentukan masa selepas itu parameter tertentu proses ini akan mengubah masa «e», iaitu, ia akan meningkat atau berkurangan kira-kira 2.718 kali. berbanding keadaan awal.

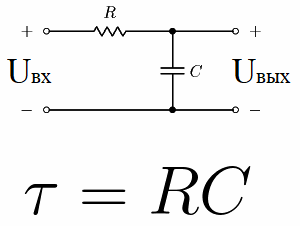

Pertimbangkan, sebagai contoh, litar elektrik yang terdiri daripada sumber voltan DC, kapasitor dan perintang. Litar jenis ini di mana perintang disambung secara bersiri dengan kapasitor dipanggil litar penyepaduan RC.

Jika pada saat permulaan masa untuk membekalkan kuasa kepada litar sedemikian, iaitu, untuk menetapkan voltan malar Uin pada input, maka Uout - voltan dalam kapasitor, akan mula berkembang secara eksponen.

Selepas masa t1, voltan kapasitor akan mencapai 63.2% daripada voltan masukan. Jadi, selang masa dari saat awal hingga t1 ialah pemalar masa litar RC ini.

Pemalar rantai ini dipanggil «tau», diukur dalam beberapa saat dan ditunjukkan oleh huruf Yunani yang sepadan. Secara berangka, untuk litar RC, ia sama dengan R * C, di mana R dalam ohm dan C dalam farad.

Litar RC penyepaduan digunakan dalam elektronik sebagai penapis laluan rendah apabila frekuensi yang lebih tinggi mesti dipotong (ditindas) dan frekuensi yang lebih rendah mesti melaluinya.

Dalam amalan, mekanisme penapisan sedemikian adalah berdasarkan prinsip berikut. Untuk arus ulang alik, kapasitor bertindak sebagai rintangan kapasitif, yang nilainya berkadar songsang dengan frekuensi, iaitu, semakin tinggi frekuensi, semakin rendah reaktansi kapasitor dalam ohm.

Oleh itu, jika arus ulang alik dialirkan melalui litar RC, maka, seperti pada lengan pembahagi voltan, voltan tertentu akan jatuh merentasi kapasitor, berkadar dengan kapasitansinya pada frekuensi arus yang dilalui.

Jika kekerapan potong dan amplitud isyarat berselang-seli input diketahui, maka tidak sukar bagi pereka bentuk untuk memilih kapasitor dan perintang sedemikian dalam litar RC, supaya voltan minimum (cut-off) (untuk kekerapan potong - had atas frekuensi) jatuh pada kapasitor, kerana reaktansi memasuki pembahagi bersama-sama dengan perintang.

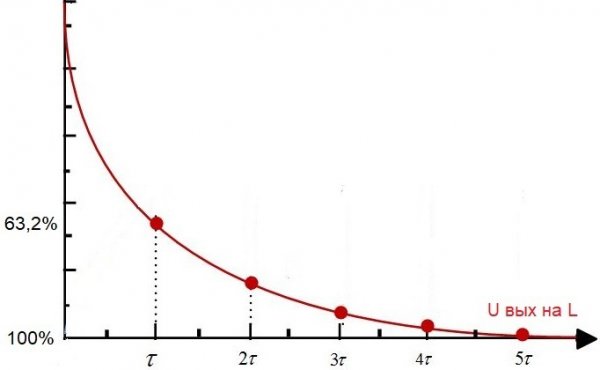

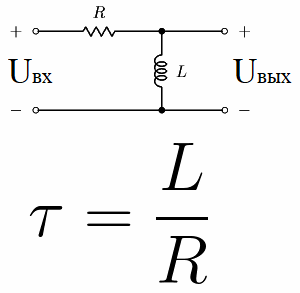

Sekarang pertimbangkan apa yang dipanggil litar pembezaan. Ia adalah litar yang terdiri daripada perintang dan induktor yang disambung secara bersiri, litar RL. Pemalar masanya secara berangka sama dengan L / R, di mana L ialah kearuhan gegelung dalam henries dan R ialah rintangan perintang dalam ohm.

Jika voltan malar daripada punca dikenakan pada litar sedemikian, selepas beberapa lama tau voltan gegelung akan berkurangan berbanding U dalam sebanyak 63.2%, iaitu mengikut penuh nilai pemalar masa untuk litar elektrik ini. .

Dalam litar AC (isyarat berselang-seli), litar LR digunakan sebagai penapis laluan tinggi apabila frekuensi rendah mesti dipotong (ditindas) dan frekuensi di atas (di atas frekuensi pemotongan — had frekuensi rendah) — ditinggalkan.Jadi, semakin tinggi induktansi gegelung, semakin tinggi frekuensinya.

Seperti dalam kes litar RC yang dibincangkan di atas, prinsip pembahagi voltan digunakan di sini. Arus frekuensi yang lebih tinggi yang melalui litar RL akan mengakibatkan penurunan voltan yang lebih besar merentasi kearuhan L, seperti rintangan induktif yang merupakan sebahagian daripada pembahagi voltan bersama-sama dengan perintang. Tugas pereka bentuk adalah untuk memilih R dan L sedemikian supaya voltan minimum (sempadan) gegelung diperoleh tepat pada frekuensi sempadan.